# Simulink<sup>®</sup> PLC Coder™ Reference

# MATLAB&SIMULINK®

R

**R**2022**b**

# **How to Contact MathWorks**

Latest news:

Phone:

www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

$\searrow$

508-647-7000

#### The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Simulink<sup>®</sup> PLC Coder<sup>™</sup> Reference

© COPYRIGHT 2019-2022 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ {\tt products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ {\tt see\ www.mathworks.com/patents\ for\ more\ information.}$

#### **Revision History**

| March 2019Online onlySeptember 2019Online onlyMarch 2020Online onlySeptember 2020Online onlyMarch 2021Online onlySeptember 2021Online onlyMarch 2022Online onlySeptember 2022Online onlySeptember 2022Online only | New for Version 3.0 (Release 2019a)<br>Revised for Version 3.1 (Release 2019b)<br>Revised for Version 3.2 (Release 2020a)<br>Revised for Version 3.3 (Release 2020b)<br>Revised for Version 3.4 (Release 2021a)<br>Revised for Version 3.5 (Release R2021b)<br>Revised for Version 3.6 (Release R2022a)<br>Revised for Version 3.7 (Release R2022b) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Blocks    |

|---|-----------|

| 1 |           |

|   |           |

|   |           |

|   | Functions |

| 2 |           |

|   |           |

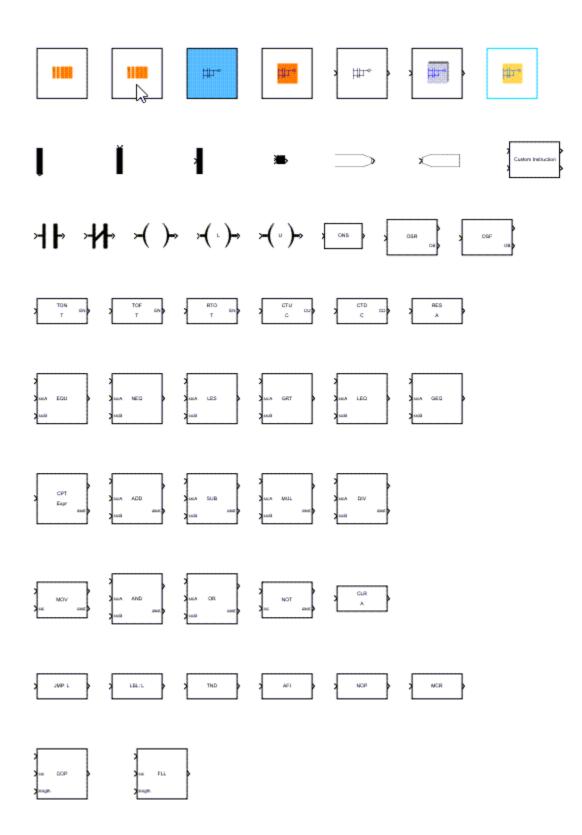

# **Blocks**

# ADD

Add inputs Library:

# Description

The ADD block implements the ADD ladder logic instruction. When the rung conditions are true, the block adds source A (srcA) to source B (srcB) and outputs the result to the destination (dest).

### Ports

### Input

#### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### srcA — First input signal

scalar

The first input signal to the addition operation.

Data Types: int8 | int16 | int32 | single

#### srcB — Second input signal

scalar

The second input signal to the addition operation.

Data Types: int8 | int16 | int32 | single

#### Output

#### EnableOut — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

dest — Output signal

scalar

#### Output signal resulting from the addition operation.

Data Types: int8 | int16 | int32 | single

### **Version History** Introduced in R2019a

# See Also

SUB | MUL | DIV | CPT

# AFI

Always False Library:

# Description

The AFI block implements the AFI ladder logic instruction. This block sets its **EnableOut** signal to false. Use this block to temporarily disable a rung while you are debugging.

### Ports

Input

#### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### Output

EnableOut — Enable Output

off (default) | on

When the block executes, it automatically sets the **EnableOut** to false. This disables the subsequent blocks on the rung.

# **Version History**

Introduced in R2019a

See Also AFI | JMP | LBL | MCR | NOP | TND

# AND

Bitwise AND Library:

# Description

The AND block implements the AND ladder logic instruction. When the rung conditions are true, the block performs bitwise AND operation on the values at source A with the values at source B. The result of this operation is available at the destination port (dest).

### Ports

#### Input

#### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### srcA — First input signal

scalar

The first input signal to the bitwise AND operation. If the datatype is single (REAL - ladder logic equivalent), the input value is converted to int32 (DINT - ladder logic equivalent). int8, int16 (SINT, INT - ladder logic equivalent) datatypes are converted to int32 (DINT - ladder logic equivalent) by filling the upper bits with 0s.

Data Types: int8 | int16 | int32 | single

#### srcB — Second input signal

scalar

The second input signal to the bitwise AND operation. If the datatype is single (REAL - ladder logic equivalent), the input value is converted to int32 (DINT - ladder logic equivalent). int8, int16 (SINT, INT - ladder logic equivalent) datatypes are converted to int32 (DINT - ladder logic equivalent) by filling the upper bits with 0s.

Data Types: int8 | int16 | int32 | single

#### Output

EnableOut — Enable Output off (default) | on By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

# dest — Output signal scalar

Output signal resulting from the bitwise AND operation. If the datatype is single (REAL - ladder logic equivalent), the resultant int32 (DINT - ladder logic equivalent) is converted to REAL (single - ladder logic equivalent).

Data Types: int8 | int16 | int32 | single

### Version History Introduced in R2019a

See Also NOT | OR

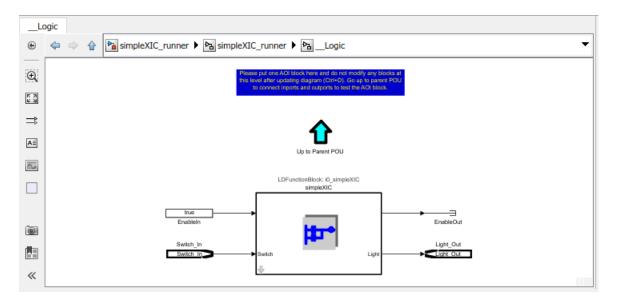

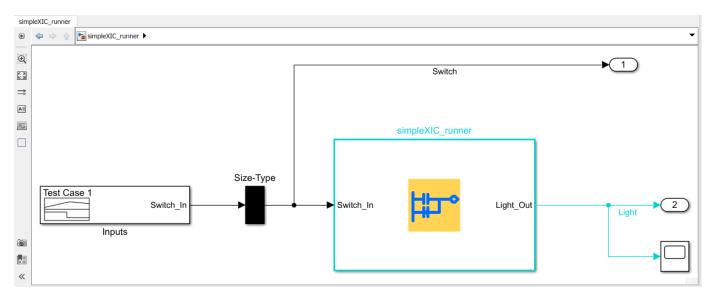

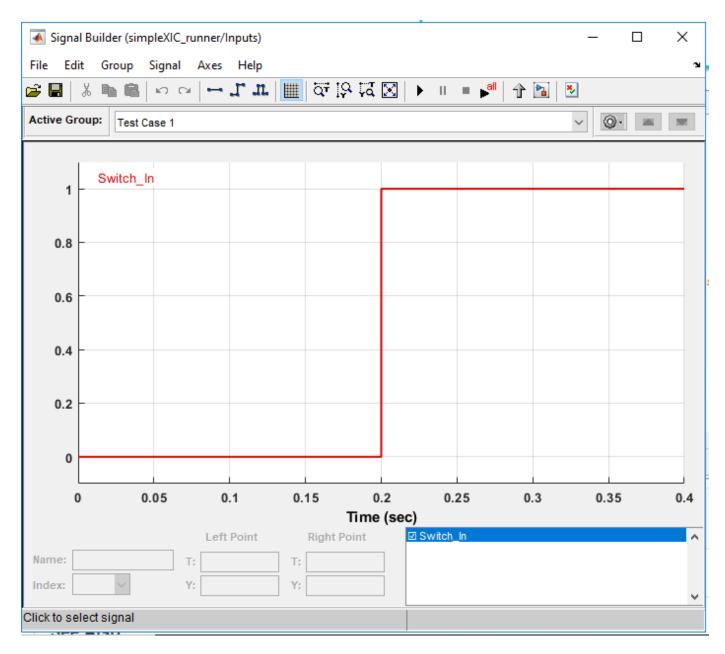

# **AOI Runner**

AOI Runner Library:

# Description

AOI Runner is a top organizational unit. It consists of AOI block. The AOI runner acts as an encapsulation around the ladder diagram function block.

# **Version History**

Introduced in R2019a

### See Also

PLC Controller | Task | Ladder Diagram Program | Ladder Diagram Subroutine | Ladder Diagram Function Block (AOI)

# CLR

Clear **Library:**

# Description

The CLR block implements the CLR ladder logic instruction. When the rung conditions are true, the block clears the bits specified in the Data To Clear tag.

# Ports

Input

#### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### Output

#### EnableOut — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

#### **Parameters**

#### Data To Clear — Operand data

A (default) | boolean

Specify the data bits to be cleared. Data bits are specified in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Data To Clear, open the **Program Variables** table within the Ladder Diagram Program block.

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'A'

# Version History Introduced in R2019a

# See Also

MOV

# ControllerTags

# Syntax

### Description

The **Controller Tags** table is used to specify the global variable and I/O symbol attributes.

For example, the controller tag table can be used to specify attributes for global variables (tags) as shown.

| 指 Block Paramet   | ers: Controller Tags |       |           |      |      |               |          | ×  |

|-------------------|----------------------|-------|-----------|------|------|---------------|----------|----|

| - Global Variable | and Symbol Spreads   | sheet |           |      |      |               |          |    |

| Name              | Mapping Type         | Port  | Data Type |      | Size | Initial Value | Delete   |    |

| Start             | Input Symbol 🔻       | 1 •   | boolean   | ~ >> | 1    | true          | ]        |    |

| Stop              | Input Symbol 🔻       | 2 •   | boolean   | ~ >> | 1    | false         | ]        |    |

| Motor             | Output Symbo 🔻       | 1 •   | boolean   | ~ >> | 1    | false         | ]        |    |

|                   |                      |       |           |      | ОК   | Cancel He     | elp Appl | ly |

# **Version History**

Introduced in R2019a

### See Also

AOI Runner | Task | Ladder Diagram Program | Ladder Diagram Subroutine | Ladder Diagram Function Block (AOI)

# СОР

#### Copy File Library:

# Description

The COP block implements the COP instruction. When the rung conditions are true, the block is used to copy the data of the source and store it at the destination, keeping the source unchanged.

# Limitations

- Source and destination elements support only numerical data types.

- Source initial element index and destination element initial index start from zero.

### Ports

#### Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

src — Source scalar | vector | matrix

It gives the value stored at source. This data is copied into destination.

Data Types: int8 | int16 | int32 | int64 | single | String | Structure

# length - Length of elements

scalar

It gives the number or source elements to copy.

Data Types: int8 | int16 | int32

#### Output

EnableOut — Enable Output off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

#### **Parameters**

#### Source Initial Element Index — Source Start Index

1 (default) | scalar

Source Start Index is used only when the source is an array. It specifies the index of the first element to be copied into destination. If the source is not an array, then the value of Source Inital Element Index is 1.

Programmatic Use Block Parameter: PLCSRCArrayIndex Type: scalar Value: scalar Default: 1

Data Types: int8 | int16 | int32 | single

#### Destination Array Name — Destination

A (default) | boolean

The data copied from source is stored in destination. The destination is specified in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Destination Array Name, open the **Program Variables** table within the Ladder Diagram Program block.

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'A'

### Destination Initial Element Index — Destination Start Index

scalar

Destination Start Index is used only when the source is an array. It specifies the start index of destination where the data is copied. If the source and destination data is not stored in an array, then the value of Destination Initial Element Index is 1.

Programmatic Use Block Parameter: PLCDestArrayIndex Type: scalar Value: scalar Default: 0

Data Types: int8 | int16 | int32 | single

# **Version History**

Introduced in R2019a

# See Also

FLL

# СРТ

Evaluate expression Library:

# Description

The CPT block implements the CPT ladder logic instruction. When the rung conditions are true, the block evaluates the expression **Expr** and outputs the result to the destination (dest).

### Limitations

• The CPT ladder diagram instruction does not support direct operand calls. Currently MOD, AND, XOR, FTD, and TOD instructions are unsupported as CPT operands.

### Ports

#### Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### Output

EnableOut — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

dest — Output Signal

scalar

The result obtained after computing the expression is placed at the destination.

Data Types: int8 | int16 | int32 | single

### **Parameters**

#### Expression to Evaluate — Expression to evaluate

'Expr' (default) | character vector

Specify the expression to be evaluated. An expression consisting of tags and/or immediate values separated by operators. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Expression to Evaluate, open the **Program Variables** table within the Ladder Diagram Program block.

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'Expr'

# **Version History**

Introduced in R2019a

#### See Also

ADD | SUB | MUL | DIV

# CTD

Count Down Library:

# Description

The CTD block implements the CTD ladder logic instruction. When the rung conditions are true, the block counts downwards.

### Ports

Input

#### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### Output

#### **CD** — Count Down Enable Output

off (default) | on

The count down enable output contains the rung-in condition when the instruction was last executed. By default, **CD** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **CD** signal is set to false.

#### **Parameters**

#### Counter Tag — Counter Structure

C (default) | character vector

Specify the counter parameters in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag, open the **Program Variables** table within the Ladder Diagram Program block. The Data Type of the timer tag is of the Bus:COUNTER type with its initial value specified as a structure containing the following fields:

| Field | Description                                                                                                                      | Default Value |

|-------|----------------------------------------------------------------------------------------------------------------------------------|---------------|

| PRE   | The preset value specifies the<br>value which the accumulated<br>value must reach before the<br>instruction indicates it is done | 0             |

| ACC   | The accumulated value specifies<br>the number of transitions the<br>instruction has counted.                                     | 0             |

| cu    | The count up enable contains<br>rung-condition-in when the<br>instruction was last executed.                                     | 1             |

| CD    | Count down enabled.                                                                                                              | 1             |

| DN    | The done bit when set indicates<br>the counting operation is<br>complete                                                         | 0             |

| 0V    | The overflow bit when set<br>indicates the counter<br>incremented past the upper<br>limit of 2,147,483,647                       | 0             |

| UN    | The underflow when set<br>indicates the counter<br>decremented past the lower<br>limit of -2,147,483,648.                        | 0             |

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'T'

# **Version History**

Introduced in R2019a

### See Also

TON | TOF | RTO | CTD | RES

# CTU

Count Up Library:

# Description

The CTU block implements the CTU ladder logic instruction. When the rung conditions are true, the block counts upwards.

### Ports

Input

#### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### Output

#### CU — Count Up Enable Output

off (default) | on

The count up enable output contains the rung-in condition when the instruction was last executed. By default, **CU** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **CU** signal is set to false.

#### **Parameters**

#### Counter Tag — Counter Structure

C (default) | character vector

Specify the counter parameters in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag, open the **Program Variables** table within the Ladder Diagram Program block. The Data Type of the timer tag is of the Bus:COUNTER type with its initial value specified as a structure containing the following fields:

| Field | Description                                                                                                                      | Default Value |

|-------|----------------------------------------------------------------------------------------------------------------------------------|---------------|

| PRE   | The preset value specifies the<br>value which the accumulated<br>value must reach before the<br>instruction indicates it is done | 0             |

| ACC   | The accumulated value specifies<br>the number of transitions the<br>instruction has counted.                                     | 0             |

| CU    | The count up enable contains<br>rung-condition-in when the<br>instruction was last executed.                                     | 1             |

| CD    | Count down enabled.                                                                                                              | 1             |

| DN    | The done bit when set indicates<br>the counting operation is<br>complete                                                         | 0             |

| 0V    | The overflow bit when set<br>indicates the counter<br>incremented past the upper<br>limit of 2,147,483,647                       | 0             |

| UN    | The underflow when set<br>indicates the counter<br>decremented past the lower<br>limit of -2,147,483,648.                        | 0             |

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'T'

# **Version History**

Introduced in R2019a

### See Also

TON | TOF | RTO | CTU | RES

# **Custom Instruction**

Create custom ladder logic instruction Library:

# Description

The Custom Instruction block implements user-defined instructions for a ladder diagram model. When the rung conditions are true, the block executes the specified custom logic. You can save these instructions in a user-defined library named plcuserlib.slx. You can also import, simulate, and export your ladder logic instructions by using your custom blocks saved in plcuserlib.slx library.

### Ports

#### Input

### EnableIn — Enable Input

off (default) | on

The **EnableIn** port controls the execution of the block and also reflects the rung state preceding the block. If the rung state preceding the block is false, the **EnableIn** signal is set to false, the block does not execute the custom logic, and the outputs are not updated.

#### src — Input signal

scalar

Input signal to the Custom Instruction block.

Data Types: int8 | int16 | int32 | single

#### Output

EnableOut — Enable Output

off (default) | on

If the **EnableIn** input to the block is false, the custom logic implemented by the block is not executed and **EnableOut** signal is set to false. If **EnableIn** is true and the custom instruction executes, **EnableOut** signal is set to true.

### **Parameters**

#### Inputs and Outputs

**Instruction Name — Name of user-defined ladder logic instruction** sampleBlock (default) | character vector Name of the ladder logic instruction that you want to create. The Rockwell Automation<sup>®</sup> Studio 5000 IDE must support the ladder logic instruction name.

#### Number of Inputs — Number of input signals to block

1 (default) | scalar

The number of input signals to the block that are required for your custom ladder logic instruction.

Programmatic Use Block Parameter: NumInputs Type: scalar Value: scalar Default: 1

Data Types: int8 | int16 | int32 | single

#### Input Types — Data type of input signal

{{'SINT', 'INT', 'DINT', 'REAL'}} (default) | character vector

The data type of the input signal specified as a cell array. For multiple inputs signals, specify the data type as a comma-separated list of cell arrays for each signal. For example, if you have two input signals with the same data type, then specify the **Input Types** as {{'SINT', 'INT', 'DINT', 'REAL'}, {'SINT', 'INT', 'REAL'}.

Programmatic Use Block Parameter: InputTypeList Type: cell array Value: cell array Default: {{'SINT', 'INT', 'DINT', 'REAL'}}

Data Types: character vector

Number of Outputs — Number of output signals from block

1 (default) | scalar

The number of output signals from the user-defined Custom Instruction block.

Programmatic Use Block Parameter: NumOutputs Type: scalar Value: scalar Default: 1

Data Types: int8 | int16 | int32 | single

#### Output Types — Data type of output signal

{{ 'SINT', 'INT', 'DINT', 'REAL'}} (default) | character vector

The data type of the output signal specified as a cell array. If there is more than one output signal, specify the data type as a comma-separated list of cell arrays for each signal. For example, if you have two output signals with the same data type, then specify the **Output Types** as {{'SINT', 'INT', 'DINT', 'REAL'}.

Programmatic Use Block Parameter: OutputTypeList Type: cell array Value: cell array Default: {{'SINT', 'INT', 'DINT', 'REAL'}}

Data Types: character vector

# **Version History**

Introduced in R2020a

### See Also

plcimportladder|plcladderinstructions

#### Topics

"Create Custom Instruction in PLC Ladder Diagram Models" "Import L5X Ladder Diagram Files into Simulink" "Model and Simulate Ladder Diagrams in Simulink" "Generating Ladder Diagram Code from Simulink"

# DIV

Divide one input by another Library:

# Description

The DIV block implements the DIV ladder logic instruction. When the rung conditions are true, the block divides the dividend at source A (srcA) by the divisor at source B (srcB) and outputs the result to the destination (dest).

**Note** If you perform a divide by zero operation a "Divide by zero detected" diagnostic message is generated during code generation.

### Ports

#### Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### srcA — First input signal

scalar

The first input signal to the division operation.

Data Types: int8 | int16 | int32 | single

#### srcB — Second input signal

scalar

The second input signal to the division operation.

Data Types: int8 | int16 | int32 | single

#### Output

**EnableOut** — **Enable Output** off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

dest — Output signal scalar

Output signal resulting from the division operation.

Data Types: int8 | int16 | int32 | single

# **Version History**

Introduced in R2019a

### See Also

ADD | SUB | MUL | CPT

# EQU

#### Equal To Library:

# Description

The EQU block implements the EQU instruction. When the rung conditions are true, the block verifies whether the value at source A is equal to the value at source B.

### Ports

#### Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

srcA — First input signal

scalar

Value to test against srcB. Data Types: int8 | int16 | int32 | single

# srcB — Second input signal

scalar

Value to test against srcA. Data Types: int8 | int16 | int32 | single

#### Output

EnableOut — Enable Output off (default) | on

If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false. If **EnableIn** is true, **EnableOut** signal is set to true, if srcA is equal to srcb.

# Version History Introduced in R2019a

# See Also

GEQ | GRT | LEQ | NEQ | LES

# FBC

File Bit Comparison Library:

# Description

The FBC block implements the FBC instruction. The block compares the source and reference data bit by bit and stores the outcome in result.

### Ports

Input

#### EnableIn — Enable Input

off (default) | on

This acts as the enabler for the block. The FBC block executes only when EnableIn is true.

#### src — Source integer

It gives the value stored at source. This value is compared with reference. Since the block performs a bit comparison, the source is an array variable.

Data Types: int32

#### ref – Reference

integer

It gives the value stored at reference. This value is compared with source. Since the block performs a bit comparison, the reference is an array variable.

Data Types: int32

res — Result integer The result of bit comparison between source and reference is stored at Result. This is an array variable.

Data Types: int32

#### compareCtrl — Compare Control

structure

It is a structure consisting of length and position variables. The length variable stores the number of bits to compare. The position variable stores the current position in the source. The initial value of position variable is 0.

#### resultsCtrl — Results Control

structure

It is a structure consisting of length and position variables. The length variable stores the number of storage locations in the result. The position variable stores the current position in the result. The initial value of position variable is 0.

#### srcIndex — Source Index

scalar

Source Start Index specifies the index of the starting element in source for comparison. Typically the value of srcIndex is 0.

Data Types: int8 | int16 | int32 | single

#### refIndex — Reference Index

scalar

Reference Start Index specifies the index of the starting element in reference for comparison. Typically the value of refIndex is 0.

Data Types: int8 | int16 | int32 | single

#### resIndex — Result Index

scalar

Result Start Index specifies the index of the starting element in result for storing the result of comparison. Typically the value of resIndex is 0.

Data Types: int8 | int16 | int32 | single

#### Output

#### EnableOut — Enable Output

off (default) | on

When set, EnableOut provides the result of the block at the output. Once EnableIn is set, it automatically sets the EnableOut.

#### resOut - Result Output

integer

The result of comparison stored in res is available at the output port. The data can be read by connecting a variable write block at resOut.

Data Types: int32

#### compareOut — Compare Output

structure

The comparison operation modifies the values of position and length variable of compareCtrl. The compareCtrl structure is available at the compareOut port. The data can be read by connecting a variable write block to it.

#### ResultsOut — Results Output

structure

The comparison operation modifies the values of position and length variable of resultsCtrl. The resultsCtrl structure is available at the resultsOut port. The data can be read by connecting a variable write block to it.

#### **Parameters**

Sample time (-1 for inherited) — Discrete interval between sample time hits

-1 (default) | scalar

Enter the discrete interval between sample time hits or specify -1 to inherit the sample time

See also "Specify Sample Time".

Programmatic Use Block Parameter: SampleTime Type: character vector Value: real scalar Default: '-1'

# **Version History**

Introduced in R2019a

See Also

# FLL

# Description

The FLL block implements the FLL instruction. When the rung conditions are true, the block fills a block of memory with the provided source value. The Source remains unchanged.

# Limitations

- Source elements should be scalar numeric data types.

- Destination elements should be scalar numeric data types.

- Source and destination elements should be of the same data type.

- Source initial element index and destination element initial index start from zero.

### Ports

#### Input

#### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

# src — Source scalar | vector | matrix

#### It gives the value stored at source. This data is copied into destination.

Data Types: int8 | int16 | int32 | int64 | single | String | Structure

#### length — Length of elements

scalar

#### Number of destination elements to fill.

Data Types: int8 | int16 | int32

#### Output

# EnableOut — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

#### **Parameters**

#### Destination Array Name — Destination

A (default) | boolean

The data copied from source is filled to the destination. The destination is specified in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Destination Array Name, open the **Program Variables** table within the Ladder Diagram Program block.

#### Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'A'

#### **Destination Initial Element Index — Destination Start Index** scalar

Destination Start Index is used only when the source is an array. It specifies the start index of destination where the data is copied. If the source and destination data is not stored in an array, then the value of Destination Initial Element Index is 1.

#### Programmatic Use Block Parameter: PLCDestArrayIndex Type: scalar Value: scalar Default: 0

Data Types: int8 | int16 | int32 | single

# **Version History**

Introduced in R2019a

See Also

# FRD

Convert to integer Library:

# Description

The FRD block implements the FRD ladder logic instruction. When the rung conditions are true, the block converts the BCD value at source A (srcA) to a decimal value and outputs the result to the destination (dest).

Note The FRD block is not supported by Simulink<sup>®</sup> Design Verifier<sup>™</sup>.

### Ports

Input

#### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### srcA — Input signal

scalar

The input value to the conversion operation.

Data Types: int8 | int16 | int32

#### Output

#### EnableOut — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

#### dest — Output signal

scalar

The decimal equivalent value of input is present at the destination.

Data Types: int8 | int16 | int32

# Version History Introduced in R2019a

# See Also

ADD | SUB | MUL | DIV | CPT

# GEQ

Greater Than or Equal To Library:

# Description

The GEQ block implements the GEQ instruction. When the rung conditions are true, the block verifies whether the value at source A is greater than or equal to the value at source B.

### Ports

Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

srcA — First input signal

scalar

Value to test against srcB. Data Types: int8 | int16 | int32 | single

# srcB — Second input signal

scalar

Value to test against srcA. Data Types: int8 | int16 | int32 | single

### Output

EnableOut — Enable Output off (default) | on

If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false. If **EnableIn** is true, **EnableOut** signal is set to true, if srcA is greater than or equal to srcb.

# Version History Introduced in R2019a

# See Also

EQU | GRT | LEQ | NEQ | LES

# GRT

Greater than Library:

# Description

The GRT block implements the GRT instruction. When the rung conditions are true, the block verifies whether the value at source A is greater than the value at source B.

### Ports

Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

srcA — First input signal

scalar

Value to test against srcB. Data Types: int8 | int16 | int32 | single

# srcB — Second input signal

scalar

Value to test against srcA. Data Types: int8 | int16 | int32 | single

### Output

EnableOut — Enable Output off (default) | on

If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false. If **EnableIn** is true, **EnableOut** signal is set to true, if srcA is greater than srcb.

# Version History Introduced in R2019a

# See Also

EQU | GEQ | LEQ | NEQ | LES

# JMP

Jump **Library:**

# Description

The JMP block implements the JMP ladder logic instruction. When the rung conditions are true, the block skips a part of ladder logic and the rung execution moves to the block referenced by the label block. Jump block can only skip the rungs after it. The block does not support a backward jump.

### Ports

Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

### Output

### EN — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

### **Parameters**

Jump to Label — Name of the label

L (default) | character vector

Specify the name for associated LBL instruction.

Programmatic Use Block Parameter: PLCLabelTag Type: character vector Value: character vector Default: 'L'

# **Version History**

Introduced in R2019a

## See Also

AFI | LBL | MCR | NOP | TND

# Junction

Junction Library:

# Description

The Junction block is used to connect one or more ladder logic branches.

# **Version History**

Introduced in R2019a

**See Also** Power Rail Start | Power Rail Terminal | Rung 1

# **Function Block (AOI)**

Ladder Diagram Function Block (AOI) Library:

### Description

The Ladder Diagram function block is a standalone, organizational unit. Use this block in the absence of a general hierarchy of controller, task, program, and ladder diagram. It is also called an AOI block. The Ladder Diagram function block consists of a ladder diagram and function block variables. The function block variables represent the function variables used in the ladder diagram and provide information about its data types, size, and initial value.

### Limitations

- Input and output variable data types must be SINT, DINT, INT, REAL, or BOOL.

- Input and output variable size must be one.

- You must not use global variables in ladder diagrams inside the Logic Routine.

### Ports

Input

#### EnableIn — Enable Input

off (default) | on

The **EnableIn** port controls the execution of the block and reflects the rung state preceding the block. If the rung state preceding the block is false, the **EnableIn** signal is set to false, the block does not execute the custom logic, and the outputs are not updated.

### Output

### EnableOut — Enable Output

off (default) | on

If the **EnableIn** input to the block is false, the custom logic implemented by the block is not executed and the **EnableOut** signal is set to false. If **EnableIn** is true and the custom instruction executes, the **EnableOut** signal is set to true.

### **Parameters**

#### **Inputs and Outputs**

#### Function Block Name — Name of AOI

FB (default) | character vector

Name of the AOI function block that you want to create. The Rockwell Automation Studio 5000 IDE must support the ladder logic instruction name.

Programmatic Use Block Parameter: PLCPOUName Type: character vector Value: character vector Default: 'FB'

#### Block Data Tag — Name of the AOI instance

D (default) | character vector

Name of the AOI instance that you want to generate code for or the instance name for the imported AOI instruction. The Rockwell Automation Studio 5000 IDE must support the ladder logic instruction name.

#### Programmatic Use

Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'D'

Variable Table — Open AOI variable table Boolean

Button that opens the AOI variable table.

#### Programmatic Use

Block Parameter: PLCEditVariableSS Type: button

Logic Routine — Open AOI ladder logic Boolean

Button that opens the ladder logic routine to implement the AOI ladder logic.

Programmatic Use Block Parameter: PLCEditPOU Type: button

# Allow EnableInFalse Routine — Enable EnableInFalse routine ladder logic Boolean

Check box that you select to enable the ladder logic inside the EnableInFalse routine.

Programmatic Use Block Parameter: PLCAllowEnableInFalse Type: check-box

# EnableInFalse Routine — Open EnableInFalse routine ladder logic Boolean

Button that opens the ladder logic routine to implement the AOI EnableInFalse ladder logic.

# Programmatic Use Block Parameter: PLCEditEnableInFalse Type: button

Allow Prescan Routine — Enable Prescan routine ladder logic Boolean

Check box that you select to enable the ladder logic inside the Prescan routine.

Programmatic Use Block Parameter: PLCAllowPrescan Type: check-box

**Prescan Routine — Open Prescan routine ladder logic** Boolean

Button that opens the ladder logic routine to implement the AOI Prescan ladder logic.

Programmatic Use Block Parameter: PLCEditPrescan Type: button

# **Version History**

Introduced in R2019a

### See Also

AOI Runner | PLC Controller | Task | Ladder Diagram Program | Ladder Diagram Subroutine | Ladder Diagram Function Block (AOI)

# Program

Ladder Diagram Program Library:

# Description

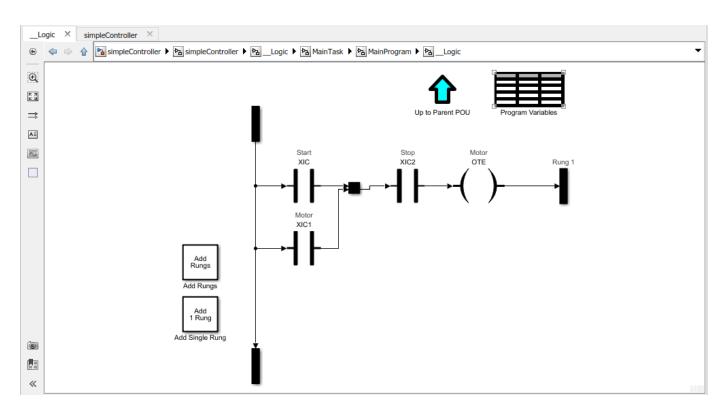

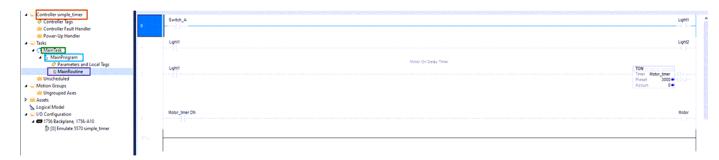

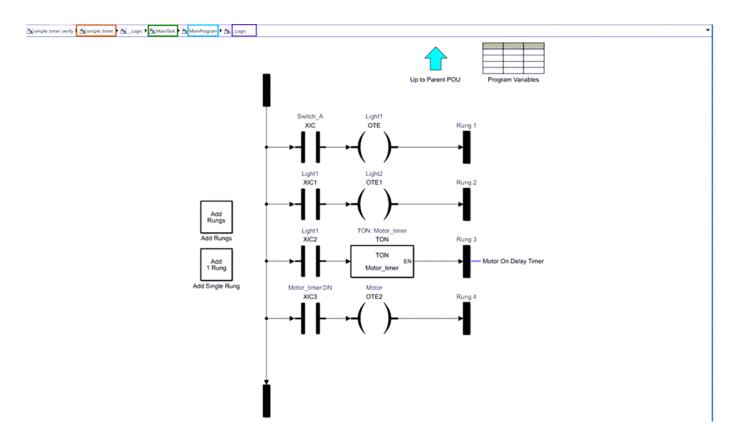

The Ladder Diagram program consists of the Ladder Diagram representation of the logic and program variables. The program executes Ladder Diagram rungs from top to bottom and from left to right. The program variables consists of local and external data types along with its data types, initial values and size. To understand the link between program structure in the Rockwell IDE and Program structure using Simulink PLC Coder refer to

### Tips

• When naming Programs choose different names for the Programs even if they are in different Tasks. Rockwell does not allow Programs to have the same names even if they are in different Tasks. For example, if you have an Input Task and Programs named Program and Program 1 these Program names will be unable for use in other Tasks in the same controller.

# **Version History**

Introduced in R2019a

### See Also

AOI Runner | PLC Controller | Task | Ladder Diagram Program | Ladder Diagram Subroutine | Ladder Diagram Function Block (AOI)

# Subroutine

Ladder Diagram Subroutine Library:

## Description

Ladder Diagram Subroutine allows you to create and define a named ladder logic routine. You can edit the logic implemented by the subroutine by clicking on the Routine Logic button found under the block parameters menu of this block.

### Ports

#### Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

### Output

### EnableOut — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

### Parameters

Routine Name — Name of the routine R (default) | character vector

Specify the name of the ladder logic subroutine.

Programmatic Use Block Parameter: PLCPOUName Type: character vector Value: character vector Default: 'R'

Routine Logic — Open ladder logic boolean

Button that opens the ladder logic subroutine.

Programmatic Use Block Parameter: PLCOpenRoutine Type: button

# **Version History**

Introduced in R2019a

### See Also

AOI Runner | PLC Controller | Task | Ladder Diagram Program | Ladder Diagram Subroutine | Ladder Diagram Function Block (AOI)

# LBL

Label **Library:**

# Description

The LBL block implements the LBL ladder logic instruction. This block is used along with JMP block. The rung execution jumps to the block referenced by LBL block.

### Ports

Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

### Output

### EN — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

### **Parameters**

Label — Name of the label L (default) | character vector

Specify the name for the LBL.

Programmatic Use Block Parameter: PLCLabelTag Type: character vector Value: character vector Default: 'L'

# **Version History**

Introduced in R2019a

### See Also

AFI | JMP | MCR | NOP | TND

# LEQ

Less Than or Equal To **Library:**

# Description

The LEQ block implements the LEQ instruction. When the rung conditions are true, the block verifies whether the value at source A is less than or equal to the value at source B.

### Ports

Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

srcA — First input signal

scalar

Value to test against srcB. Data Types: int8 | int16 | int32 | single

srcB — Second input signal

scalar

Value to test against srcA. Data Types: int8 | int16 | int32 | single

### Output

EnableOut — Enable Output off (default) | on

If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false. If **EnableIn** is true, **EnableOut** signal is set to true, if srcA is less than or equal to srcb.

# Version History Introduced in R2019a

# See Also

EQU | GEQ | GRT | NEQ | LES

# LES

Less Than **Library:**

# Description

The LES block implements the LES instruction. When the rung conditions are true, the block verifies whether the value at source A is less than the value at source B.

### Ports

Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

srcA — First input signal

scalar

Value to test against srcB. Data Types: int8 | int16 | int32 | single

srcB — Second input signal

scalar

Value to test against srcA. Data Types: int8 | int16 | int32 | single

### Output

EnableOut — Enable Output off (default) | on

If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false. If **EnableIn** is true, **EnableOut** signal is set to true, if srcA is less than srcb.

# Version History Introduced in R2019a

# See Also

EQU | GEQ | GRT | LEQ | NEQ

# MCR

Master Control Reset Library:

# Description

The MCR block implements the MCR instruction. The block simulates a master control relay that can selectively disable a section of rungs.

### Ports

Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

### Output

EnableOut — Enable Output

off (default) | on

When the block executes, it automatically sets the **EnableOut** to false. This disables all the subsequent blocks on the rung.

# **Version History**

Introduced in R2019a

**See Also** AFI | JMP | LBL | NOP | TND

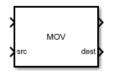

# MOV

Move Library:

## Description

The MOV block implements the MOV instruction. When the rung conditions are true, the block moves a copy of the source to the destination, keeping the source unchanged.

### Ports

Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

src — Input signal

scalar

Value to move.

Data Types: int8 | int16 | int32 | single

### Output

EnableOut — Enable Output off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

dest — Output signal scalar

Tag to store the result. Data Types: int8 | int16 | int32 | single

# **Version History**

Introduced in R2019a

# See Also

# MUL

Multiply inputs Library:

## Description

The MUL block implements the MUL ladder logic instruction. When the rung conditions are true, the block multiplies the multiplicand at source A (srcA) with the multiplier at source B (srcB) and outputs the result to the destination (dest).

### Ports

#### Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### srcA — First input signal

scalar

The first input signal to the multiplication operation.

Data Types: int8 | int16 | int32 | single

### srcB — Second input signal

scalar

The second input signal to the multiplication operation.

Data Types: int8 | int16 | int32 | single

### Output

### EnableOut — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

dest — Output signal

scalar

### Output signal resulting from the multiplication operation.

Data Types: int8 | int16 | int32 | single

# **Version History**

Introduced in R2019a

### See Also

ADD | SUB | DIV | CPT

# NEQ

Not Equal To Library:

# Description

The NEQ block implements the NEQ instruction. When the rung conditions are true, the block verifies whether the value at source A is not equal to the value at source B.

### Ports

Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

srcA — First input signal

scalar

Value to test against srcB. Data Types: int8 | int16 | int32 | single

# srcB — Second input signal

scalar

Value to test against srcA. Data Types: int8 | int16 | int32 | single

### Output

EnableOut — Enable Output off (default) | on

If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false. If **EnableIn** is true, **EnableOut** signal is set to true, if srcA is not equal to srcb.

# Version History Introduced in R2019a

# See Also

EQU | GEQ | GRT | LEQ | LES

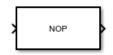

# NOP

No Operation Library:

## Description

The NOP block implements the NOP function. The block acts as a placeholder. It performs no operation on enable or disable.

### Ports

Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

### Output

EnableOut — Enable Output

off (default) | on

When the block executes, it automatically sets the **EnableOut** to false. This disables all the subsequent blocks on the rung.

# **Version History**

Introduced in R2019a

See Also AFI | JMP | LBL | MCR | TND

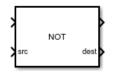

# NOT

Bitwise NOT Library:

## Description

The NOT block implements the NOT ladder logic instruction. When the rung conditions are true, the block performs bitwise NOT operation on the values at source. The result of this operation is available at the destination port (dest).

### Ports

### Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

### src — Input signal

scalar

The input signal on which to perform the bitwise NOT operation. If the datatype is single (REAL - ladder logic equivalent), the input value is converted to int32 (DINT - ladder logic equivalent). int8, int16 (SINT, INT - ladder logic equivalent) datatypes are converted to int32 (DINT - ladder logic equivalent) by filling the upper bits with 0s.

Data Types: int8 | int16 | int32 | single

### Output

### EnableOut — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

#### dest — Output signal

scalar

Output signal resulting from the bitwise NOT operation. If the datatype is single (REAL - ladder logic equivalent), the resultant int32 (DINT - ladder logic equivalent) is converted to REAL (single - ladder logic equivalent).

Data Types: int8 | int16 | int32 | single

# **Version History**

Introduced in R2019a

See Also AND | OR

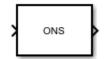

# ONS

One Shot Library:

# Description

The ONS block implements the ONS instruction. The block makes the remainder of the rung true every time the rung-condition-in transitions from false to true.

### Ports

Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

### Output

### EN — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

### **Parameters**

### Storage Bit — Internal storage bit

SB (default) | boolean

Internal storage bit that retains the rung-condition-in from the last time the instruction was executed. Specified in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag, open the **Program Variables** table within the Ladder Diagram Program block.

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'SB'

# Version History Introduced in R2019a

See Also OSR | OSF

# OR

Bitwise OR Library:

## Description

The OR block implements the OR ladder logic instruction. When the rung conditions are true, the block performs bitwise OR operation on the values at source A with the values at source B. The result of this operation is available at the destination port (dest).

### Ports

### Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

### srcA — First input signal

scalar

The first input signal to the bitwise OR operation. If the datatype is single (REAL - ladder logic equivalent), the input value is converted to int32 (DINT - ladder logic equivalent). int8, int16 (SINT, INT - ladder logic equivalent) datatypes are converted to int32 (DINT - ladder logic equivalent) datatypes are converted to int32 (DINT - ladder logic equivalent) by filling the upper bits with 0s.

Data Types: int8 | int16 | int32 | single

### srcB — Second input signal

scalar

The second input signal to the bitwise OR operation. If the datatype is single (REAL - ladder logic equivalent), the input value is converted to int32 (DINT - ladder logic equivalent). int8, int16 (SINT, INT - ladder logic equivalent) datatypes are converted to int32 (DINT - ladder logic equivalent) by filling the upper bits with 0s.

Data Types: int8 | int16 | int32 | single

### Output

**EnableOut** — **Enable Output** off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

# dest — Output signal scalar

Output signal resulting from the bitwise OR operation. If the datatype is single (REAL - ladder logic equivalent), the resultant int32 (DINT - ladder logic equivalent) is converted to REAL (single - ladder logic equivalent).

Data Types: int8 | int16 | int32 | single

### Version History Introduced in R2019a

See Also AND | NOT

# OSF

One Shot Falling Library:

## Description

The OSF block implements the **OSF** instruction. The block sets the output bit for one scan when the rung-condition-in transitions from true to false.

### Ports

Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

### Output

### EN — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

### 0B — Output Bit

boolean

Bit to be modified when the rung-condition-in transitions from false to true.

Data Types: Boolean

### **Parameters**

### Storage Bit — Internal storage bit

SB (default) | boolean

Internal storage bit that retains the rung-condition-in from the last time the instruction was executed. Specified in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag, open the **Program Variables** table within the Ladder Diagram Program block.

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'SB'

# **Version History**

Introduced in R2019a

See Also

ONS | OSR

## OSR

One Shot Rising Library:

### Description

The OSR block implements the **OSR** instruction. The block sets the output bit for one scan when the rung-condition-in transitions from false to true.

### Ports

Input

#### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### Output

### EN — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

#### 0B — Output Bit

boolean

Bit to be modified when the rung-condition-in transitions from false to true.

Data Types: Boolean

### **Parameters**

#### Storage Bit — Internal storage bit

SB (default) | boolean

Internal storage bit that retains the rung-condition-in from the last time the instruction was executed. Specified in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag, open the **Program Variables** table within the Ladder Diagram Program block.

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'SB'

## **Version History**

Introduced in R2019a

See Also

ONS | OSF

## ΟΤΕ

Output Energize Library:

### Description

**OTE** is one of the building blocks of a ladder diagram. The OTE block implements the **OTE** ladder logic instruction. The block examines the state of the rung-condition-in and sets or clears the operand tag (data bit). If rung condition is true, the block sets the data bit to true.

### Parameters

### Operand Tag — Bit to be tested

A (default) | boolean

Specify the data bits to be modified. Data bits are specified in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag, open the **Program Variables** table within the Ladder Diagram Program block.

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'A'

## **Version History**

Introduced in R2019a

See Also XIC | XIO | OTL | OTU

## OTL

Output Latch Library:

≻( ∟)→

### Description

**OTL** is one of the building blocks of a ladder diagram. The OTL block implements the **OTL** ladder logic instruction. When the rung condition is true, the block sets the operand tag (data bit) to true. The data bit remains true until it is cleared, typically by an OTU block. When the rung condition is changed to false, the block does not change the status of the data bit.

### **Parameters**

#### Operand Tag — Bit to be tested

A (default) | boolean

Specify the data bits to be modified. Data bits are specified in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag, open the **Program Variables** table within the Ladder Diagram Program block.

#### Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector

Default: 'A'

## **Version History**

Introduced in R2019a

## See Also

XIC | XIO | OTE | OTU

## ΟΤυ

Output Unlatch Library:

≻( )→

### Description

**OTU** is one of the building blocks of a ladder diagram. The OTU block implements the **OTU** ladder logic instruction. When the rung condition is true, the block clears the operand tag (data bit) to false. When the rung condition is changed to false, the block does not change the status of the data bit. It is generally used after the OTL block to unlatch the state and disable the rung.

### **Parameters**

#### Operand Tag — Bit to be tested

A (default) | boolean

Specify the data bits to be modified. Data bits are specified in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag, open the **Program Variables** table within the Ladder Diagram Program block.

#### Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'A'

**Version History**

Introduced in R2019a

See Also XIC | XIO | OTE | OTL

## **PLC Controller**

PLC Controller Library:

### Description

In Ladder Diagram, the controller is a top organisational unit that typically consists of task and controller tags. There can be a single task or multiple tasks. Tasks inside a controller are executed in parallel. There are two types of controller blocks available in Simulink PLC Coder<sup>TM</sup>:

- PLC Controller Suite

- PLC Controller

PLC controller suite is a block hierarchy that models a simple complete Ladder Logic Controller structure whereas a PLC controller block consists of ladder logic semantics. The controller tags store the information of global variables such as DataType, Mapping type, Port, Address etc. The global variables defined for a ladder diagram form the input and output ports of the controller.

## **Version History**

Introduced in R2019a

### See Also

AOI Runner | Task | Ladder Diagram Program | Ladder Diagram Subroutine | Ladder Diagram Function Block (AOI)

## **PLC Controller Suite**

PLC Controller Library:

### Description

In Ladder Diagram, the controller is a top organisational unit that typically consists of task and controller tags. There can be a single task or multiple tasks. Tasks inside a controller are executed in parallel. There are two types of controller blocks available in Simulink PLC Coder:

- PLC Controller Suite

- PLC Controller

PLC controller suite is a block hierarchy that models a simple complete Ladder Logic Controller structure whereas a PLC controller block consists of ladder logic semantics. The controller tags store the information of global variables such as DataType, Mapping type, Port, Address etc. The global variables defined for a ladder diagram form the input and output ports of the controller.

## **Version History**

### See Also

AOI Runner | Task | Ladder Diagram Program | Ladder Diagram Subroutine | Ladder Diagram Function Block (AOI)

## **Power Rail Start**

Power Rail Start Library:

## Description

The block is for reference purpose only. Do not use this block for ladder diagram modeling.

## **Version History**

Introduced in R2019a

See Also Power Rail Terminal | Junction | Rung 1

## **Power Rail Terminal**

Power Rail Terminal Library:

## Description

The block is for reference purpose only. Do not use this block for ladder diagram modeling.

## **Version History**

Introduced in R2019a

### See Also

Power Rail Start | Junction | Rung 1

## **ProgramVariables**

### Syntax

### Description

The **Program Variables** table within the Ladder Diagram Program block contains attributes associated with tags. The tags can have attributes such as Data Type, Initial Value, and size.

For example, the program variables table can be used to specify attributes for variables (tags) as shown.

| 🔁 Block Parameters: Program Variables 🛛 🕹 |           |           |        | $\times$             |   |

|-------------------------------------------|-----------|-----------|--------|----------------------|---|

| Program Variable Spreadsheet              |           |           |        |                      |   |

| Name                                      | Scope     | Data Type | Size   | Initial Value Delete |   |

| Motor                                     | Externa 🔻 |           |        |                      |   |

| Start                                     | Externa 🔻 |           |        |                      |   |

| Stop                                      | Externa 🔻 |           |        |                      |   |

|                                           |           |           |        |                      |   |

|                                           |           | ОК        | Cancel | Help Appl            | у |

## **Version History**

Introduced in R2019a

### See Also

AOI Runner | Task | Ladder Diagram Program | Ladder Diagram Subroutine | Ladder Diagram Function Block (AOI)

## RES

Reset Library:

### Description

The RES block implements the RES ladder logic instruction. When the rung conditions are true, the block resets the value of TIMER, COUNTER, or a CONTROL structure.

### Ports

Input

### EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### Output

#### EN — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

### **Parameters**

#### **Operand Tag To Reset — Structure to Reset**

A (default) | character vector

Specify the tag to reset. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag To Reset, open the **Program Variables** table within the Ladder Diagram Program block.

Programmatic Use Block Parameter: PLCTagToReset Type: character vector Value: character vector Default: 'A'

**Tag Structure – Structure Type** 'TIMER or COUNTER' (default) | 'CONTROL' Specify the structure type to reset.

| Туре             | Description                            |

|------------------|----------------------------------------|

| TIMER or COUNTER | Clears the ACC field of the structure. |

| CONTROL          | Clears the POS field of the structure. |

Programmatic Use Block Parameter: PLCTagDataType Type: character vector Value: 'TIMER or COUNTER'|'CONTROL' Default: 'TIMER or COUNTER'

## **Version History**

Introduced in R2019a

### See Also

TON | TOF | RTO | CTU | CTD

## RET

Return Library:

### Description

The RET block implements the RET instruction. The blocks is used to return the control of execution from a subroutine. It can be used only inside a subroutine. This block does not support parameters to be passed from the subroutine.

### **Parameters**

Sample time (-1 for inherited) — Discrete interval between sample time hits

-1 (default) | scalar

Enter the discrete interval between sample time hits or specify -1 to inherit the sample time

See also "Specify Sample Time".

Programmatic Use Block Parameter: SampleTime Type: character vector Value: real scalar Default: '-1'

## **Version History**

Introduced in R2019a

See Also

## RTO

Retentive Timer On Library:

### Description

The RTO block implements the **RTO** ladder logic instruction. When the rung conditions are true, the block accumulates time until:

- The timer is disabled

- The timer completes

### Ports

#### Input

EnableIn — Enable Input

off (default) | on

Controls the execution of the block. **EnableIn** reflects the rung state preceding the block. If the rung state preceding the block is false, **EnableIn** is false, the block does not execute and the outputs are not updated.

#### Output

EN — Enable Output

off (default) | on

By default, **EnableOut** follows the state of **EnableIn**. If the **EnableIn** input to the block is false, the logic implemented by the block is not executed and **EnableOut** signal is set to false.

### **Parameters**

#### Timer Tag — Timer Structure

T (default) | character vector

Specify the timer parameters in the format of tags. In Ladder Diagrams, tags (variables) are used to represent inputs, outputs, and internal memory with attributes such as Data Type, Initial Value, and size. To change the attributes of the Operand Tag, open the **Program Variables** table within the Ladder Diagram Program block. The Data Type of the timer tag is of the Bus:TIMER type with its initial value specified as a structure containing the following fields:

| Field | Description                                                                                                                                               | Default Value |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| PRE   | The preset value specifies the<br>value (1 millisecond units)<br>which the accumulated value<br>must reach before the<br>instruction indicates it is done | 0             |

| ACC   | The accumulated value specifies<br>the number of milliseconds that<br>have elapsed since the RTO<br>instruction was enabled.                              | 0             |

| EN    | The enable bit contains rung-<br>condition-in when the<br>instruction was last executed.                                                                  | 0             |

| ТТ    | The timing bit when set<br>indicates the timing operation is<br>in process.                                                                               | 0             |

| DN    | The done bit when set indicates<br>the timing operation is complete<br>(or paused).                                                                       | 0             |

Programmatic Use Block Parameter: PLCOperandTag Type: character vector Value: character vector Default: 'T'

## **Version History**

Introduced in R2019a

### See Also

TON | TOF | CTU | CTD | RES

## RungTerminal

Rung Terminal Library:

## Description